14Nov.2025

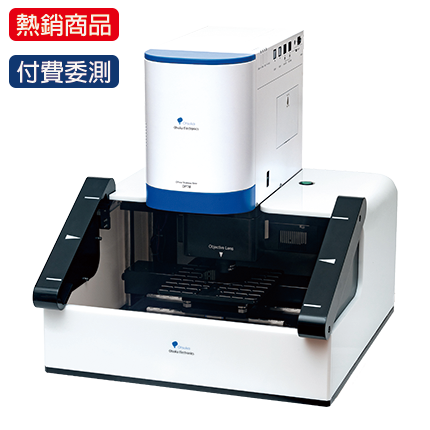

膜厚儀

Wafer是什麼?前後2大半導體製程,帶你掌握晶圓的祕密!

| 目錄 1.Wafer是什麼?搞懂晶圓、裸晶與晶片在半導體製程中的關係 2.半導體製程是什麼?為什麼晶圓(Wafer)是圓的? 3.Wafer怎麼做?半導體製程中的每一步都是關鍵! a.前段製程 b.後段製程 4.半導體製程各階段的檢測標準一次看! 5.粒徑分析及膜厚量測在半導體製程中,扮演的角色為何? |

許多人對於半導體產業不熟悉,尤其是對半導體製程的概念更是一知半解?!其實,主要是用來製作晶片的半導體製程,是需要透過一系列的專業步驟與搭配粒徑以及膜厚量測後,才能被完整運用在各產業。若你對半導體製程或Wafer還不清楚,不妨一起透過本篇介紹來快速掌握!

Wafer是什麼?搞懂晶圓、裸晶與晶片在半導體製程中的關係

在半導體製程的產業中,「晶圓(Wafer)」是一切電子元件的基礎。它是一片由高純度矽(Si)製成的薄片,作為電路製作的基板。在晶圓上經過光刻、蝕刻、鍍膜、摻雜等步驟形成電路,完成後會切割成單顆「裸晶(Die)」,再經過封裝與測試成為可實際使用的「晶片(Chip)」。其3者的關係可歸納如下:晶圓(Wafer):半導體製程的原始基板

裸晶(Die):晶圓上完成電路的單顆晶粒

晶片(Chip):封裝後的最終電子元件

半導體製程是什麼?為什麼晶圓(Wafer)是圓的?

所謂的「半導體」,其實就是指一種材料。且其具有介於導體(如:銅和鋁)和絕緣體(如:塑料和橡膠)之間的導電特性。而「半導體」的導電性能,可透過外加電場或調整內部電荷狀態來控制。當「半導體」受到外部激勵(如:電場、熱能或光照)時,價帶中的電子可被激發至導帶,就會形成自由移動的電子和正空穴(缺少電子的位置)。

這些自由移動的電子和空穴,共同決定半導體的導電性。通過控制半導體材料中的電子和空穴的數量和移動性,可實現對電流和電壓的精確控制,這是半導體器件(如:二極體、晶體管和集成電路)的基礎。而「半導體」的特性,使其在現代電子技術中扮演了重要的角色。半導體器件的不同組合和配置可以實現各種功能,從電腦和手機到家用電器和汽車等各種應用。

揭密Wafer與半導體製程的祕密

晶圓之所以是圓形,並非設計巧合,而是源自其製造方式。在半導體材料製程中,首先以「直拉法(Czochralski Method)」或「區熔法(Float Zone Method)」將高純度矽熔融後拉出長條狀的單晶矽錠(Ingot)。這個矽錠本身為圓柱形,為了最大化材料利用率並保持均勻結構,後續會再以精密設備切成薄片,即為常見的圓形晶圓(Wafer)。此外,圓形的設計可減少製程中邊角應力集中,可避免在高溫或旋轉處理的曝光/鍍膜製程中較不易產生裂紋。

半導體製程中使用到的主材料有哪些?

「半導體」材料中,最常見的是矽(silicon),而「矽」也是製造積體電路的主要材料。除此之外,還有其他半導體材料,如:砷化鎵(gallium arsenide)、砷化銦(indium arsenide)等材料。「半導體」的導電性質,與其晶體結構、電子能帶結構有關。在純淨的「半導體」中,其電子能帶結構可以劃分為價帶(valence band)和傳導帶(conduction band);價帶多為已佔據電子,導帶則電子較少。兩者之間的能隙(band gap)決定了材料的導電特性。

Wafer怎麼做?半導體製程中的每一步都是關鍵!

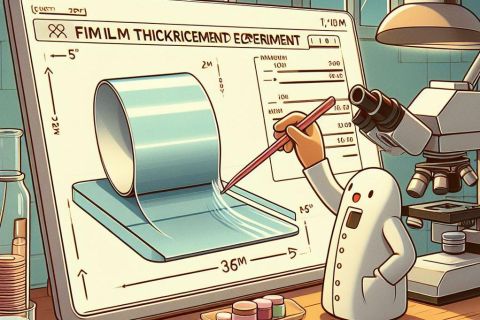

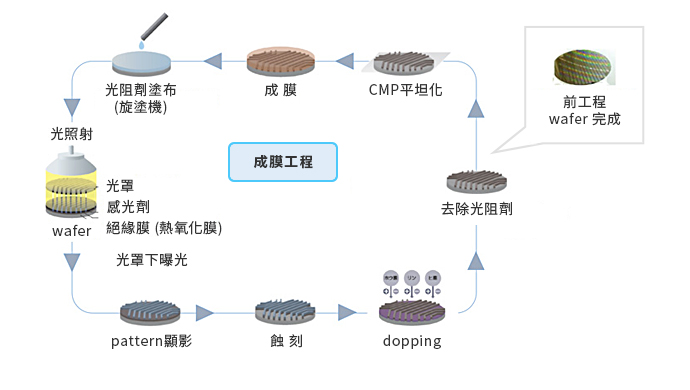

晶圓的製造是一個極度精密、層層把關的過程,主要分為以下步驟:前段製程(Front-End Process),著重於晶圓上製作電路;後段製程(Back-End Process),包含測試、切割與封裝等。前段製程涵蓋材料純化、晶圓形成、氧化、摻雜、光刻、蝕刻與薄膜沉積等程序,是決定晶片性能的核心階段。在這些製程中,光學膜厚量測、表面粗糙度分析與界面結構觀察是不可或缺的品質控管手段。

👉前段製程包括:晶圓的製造包含以下主要階段,屬於半導體的前段製程(Front-End Process)中最初的基材工程。

STEP1. 矽原料提純與長晶(Ingot製造)

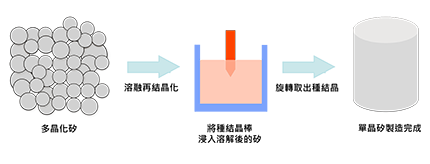

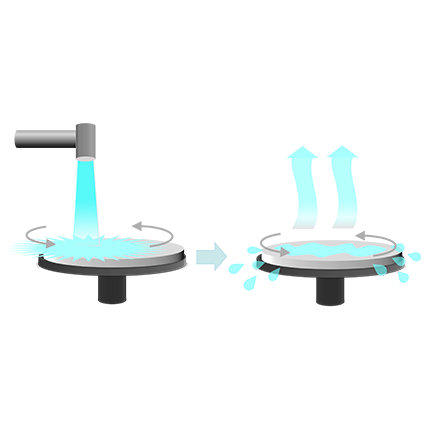

首先是「單晶矽製造」,製造晶錠作為製造晶圓的基板。多晶矽與硼(B)、磷(P)一起放入石英坩堝中,在高溫下熔化。將種晶棒浸入熔融矽液面,邊旋轉邊緩慢拉起,即可完成與種晶具有相同原子排列的單晶錠。使用石英砂精煉矽原料,經還原與提純後達電子級純度(9N 以上)。使用直拉法(CZ法)生長單晶矽棒,確保晶向與電性一致。

✅量測需求:晶體電阻率、缺陷密度、結晶方向。

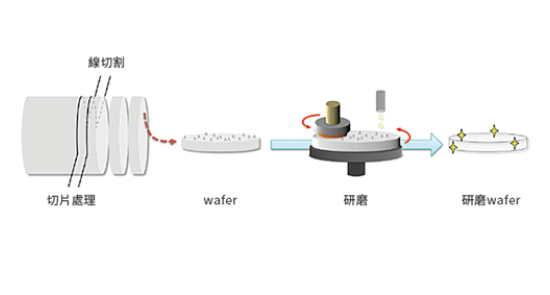

STEP2. 晶圓Wafer製作

接下來,將單晶矽棒切割成薄片(Slicing),經研磨與化學機械拋光(CMP)後,形成高平坦度鏡面。由於切割後的晶圓表面存在凹凸不平,故通過稱為研磨(粗拋光)、蝕刻(化學拋光)和拋光(鏡面拋光)的拋光工藝去除不平坦。並讓拋光後的晶圓厚度符合SEMI標準等相關標準,例如:12吋的晶圓指定厚度為775μm±20μm。

✅量測需求:厚度均勻度、平坦度、表面粗糙度、反射率。

📖 延伸閱讀:

STEP3. 晶圓洗淨(Wafer洗淨)

利用超純水與化學溶液去除拋光殘渣與金屬微粒汙染。 晶圓上的異物,會導致後續的晶體生長和光刻工藝出現缺陷。 清洗時,用雙氧水、鹽酸、氫氟酸等清洗液去除晶圓上的顆粒、金屬和有機物。之後再以超純水沖洗化學溶液後再旋乾;若仍殘留水分,易吸附空氣中顆粒。空氣中的顆粒,即使洗過也會使它再次變髒。

✅量測需求:顆粒汙染檢測、表面潔淨度分析。

📖 延伸閱讀:Wafer表面電位(ELSZ)

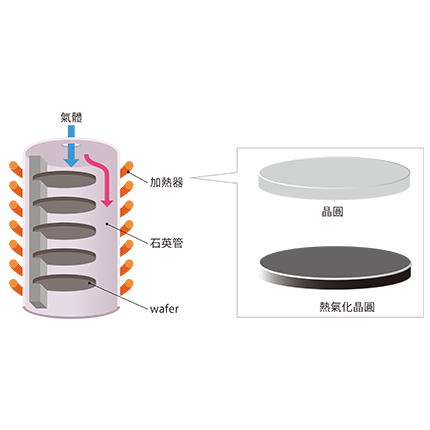

STEP4. 表面氧化(Surface Oxidation)

於高溫氧化爐中生成氧化矽層(SiO₂),作為絕緣層或光刻底層。氧化設備主要有立式爐、臥式爐、RTP設備,在稱為氧化爐的電爐中,升溫(約800℃以上),通入含氧氣體,使氧化膜生長。

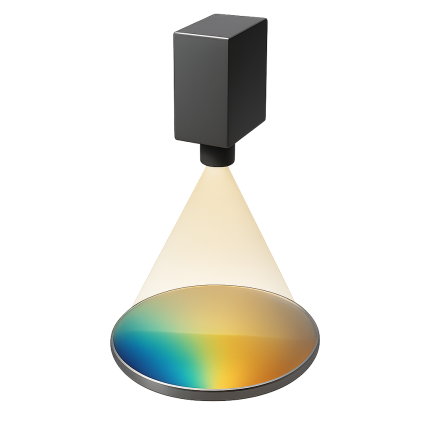

✅量測需求:氧化層膜厚、折射率、均勻性。

📖 延伸閱讀:成膜後Wafer面內膜厚分布(TE)

STEP5. 配線圖形化(Patterning)

熱氧化後,在晶圓上塗上光刻膠,並透過光刻(Photolithography)與蝕刻(Etching)在晶圓上建立電路圖形。

✅量測需求:線寬(Critical Dimension, CD)、步高差(Step Height)、膜厚分佈。

📖 延伸閱讀:

後段半導體製程步驟有哪些?從Wafer到封裝測試,完整解說!

👉後段製程(Back-End)包括:

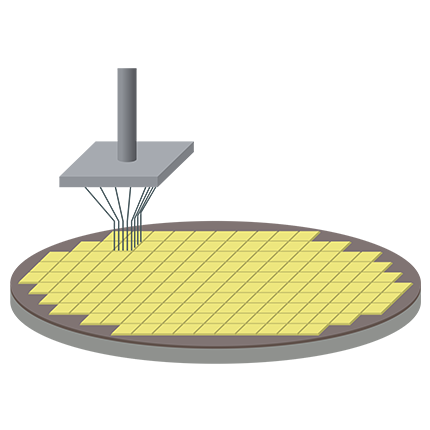

STEP1. 晶圓測試(Wafer Test)

使用探針卡測試每顆晶粒功能與電性,可測試晶圓上所有晶片的電性,並據此分揀良品與不良品。

✅量測需求:導通電阻、接觸品質、電性異常檢測。

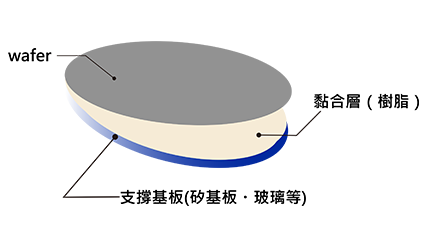

STEP2. 晶圓貼合(Wafer Bonding)

在晶圓減薄工藝中,晶圓附著在矽或玻璃等支撐基板上,以便於運輸過程中的處理。常見有樹脂(黏合層)介接,以及近年的晶片直接鍵合兩種方式。也就是將兩片晶圓貼合,用於3D堆疊或感測器製程。

✅量測需求:貼合對準精度、界面平整度、貼合強度。

📖 延伸閱讀:貼合Wafer厚度(SF-3)

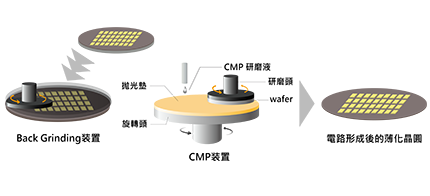

STEP3. 背面研削(Back Grinding)

在晶圓表面完成圖形後,對晶圓的整個背面進行研磨以降低厚度(通常100µm以下)以利封裝,須將磨削後的整體厚度不均控制在極小範圍內。

✅量測需求:厚度量測、翹曲控制、表面平整度。

📖 延伸閱讀:

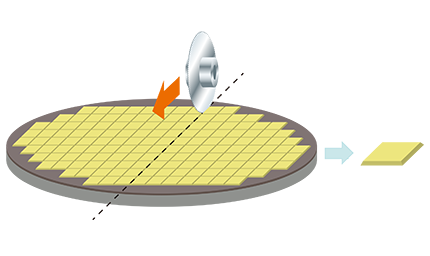

STEP4. 切割(Dicing)

將前工序中生產的晶圓,被分離成單獨的IC芯片並密封在封裝中,這種將晶圓分離為單顆 IC 裸晶的過程稱為「切割(Dicing)」。在切割時,主要使用雷射或鑽石刀將晶圓分割成單顆裸晶(Die),切割時再用純淨水冷卻並沖走切屑。

✅量測需求:切割精度、邊緣缺陷分析、尺寸偏差。

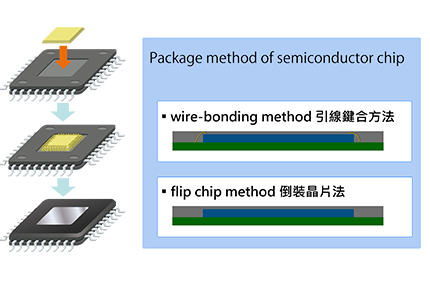

STEP5. 封裝(Packaging)

完成的晶片透過引線鍵合(Wire Bonding)或重佈線層(RDL)連接至封裝或矽中介層,將裸晶固定於基板並進行鍵合與封裝保護。

✅量測需求:封裝厚度、焊點品質、氣密性檢查。

STEP6. 組裝與最終測試(Assembly & Final Test)

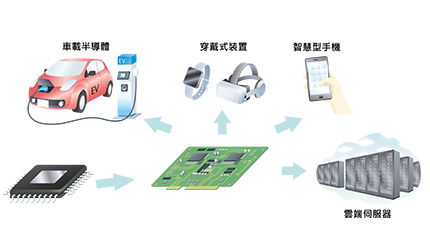

將封裝好的晶片整合至模組或系統中,進行功能與可靠度測試。完成的半導體封裝,被整合到各個領域的產品中,例如:汽車、智能手機、IoT 設備、雲端數據中心和AI相關產品。

✅量測需求:熱應力測試、性能穩定度、界面變化觀察。

半導體製程各階段的檢測標準一次看!

在半導體生產的每一階段,光學量測技術都是品質與良率控制的關鍵。大塚科技以50年光學量測經驗,提供涵蓋表面平坦度、膜厚、粒徑、界面電位等多項檢測方案。其主要應用包含:| 製程階段 | 對應量測與產品事例 | 對應產品連結 |

|---|---|---|

| Wafer製造 | SF-3 系列用於膜厚與平坦度測定,確保晶圓厚度與邊緣形狀一致 | 分光干涉式Wafer晶圓測厚儀SF-3 |

| CMP晶圓洗淨 | ELSZ neo 進行晶圓電位/粒徑量測 | 界達電位雷射粒徑分析儀ELSZneo |

| 表面氧化與薄膜形成 | 膜厚線上系統監控氧化矽薄膜膜厚與沉積均勻度 | 顯微分光膜厚量測儀OPTM series 晶圓厚度&薄膜厚量測設備產線Stand-alone型 TE series |

| 配線圖形化與CMP | 膜厚線上系統監控系統即時監測化學機械研磨中的膜厚變化 | 分光干涉式Wafer晶圓測厚儀SF-3 晶圓厚度&薄膜厚量測設備產線Stand-alone型 TE series |

| 貼合與背研 | 研磨後貼合晶圓厚度量測系統,用於3D封裝厚度控制 | 分光干涉式Wafer晶圓測厚儀SF-3-大塚科技 |

粒徑分析及膜厚量測在半導體製程中,扮演的角色為何?

由上述可得知,半導體製程從長晶到完成部件為止,需要經過多道製程。每一道製程的良率,都關乎最後產品的性能。其中,例如:研磨液的界達電位、粒徑影響研磨的過程,研磨製程後及貼合、表面氧化等也都需要監控膜厚。

「半導體」多道製程中,都有減薄、平坦化的過程,此工法又稱為「化學機械研磨,Chemical-Mechanical Polishing」,簡稱為 CMP。想知道更多有關於 CMP 的相關知識,也可以參考《CMP是什麼意思?製程深入介紹,清楚瞭解技術與原理!》這篇文章喔!

📖 閱讀更多相關文章📖

📖《CMP是什麼意思?製程深入介紹,清楚瞭解技術與原理!》相關產品

其他相關訊息

-

10.Jul.2025

PVA膜是什麼?4大應用領域要了解,掌握膜厚均勻避免誤差!

-

25.Mar.2025

半導體薄膜製程是什麼?6大技術提升良率,專業應用優勢多!

-

29.Aug.2024

光學膜(Optical Film)是什麼?6大產業應用要知道,推薦機型看這邊!