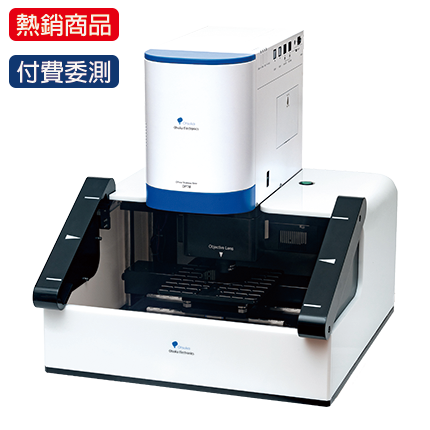

LineScan

LineScan wafer檢測系統

該裝置可在半導體研發和生產現場對晶圓基板上的薄膜整個表面進行測量。

透過獨有的光譜干涉法與新開發的高精度膜厚計算處理技術結合,可以快速測量12吋晶圓的面內分佈。

透過獨有的光譜干涉法與新開發的高精度膜厚計算處理技術結合,可以快速測量12吋晶圓的面內分佈。

量測項目

- 膜厚

產品資訊

Line scan量測原理 |

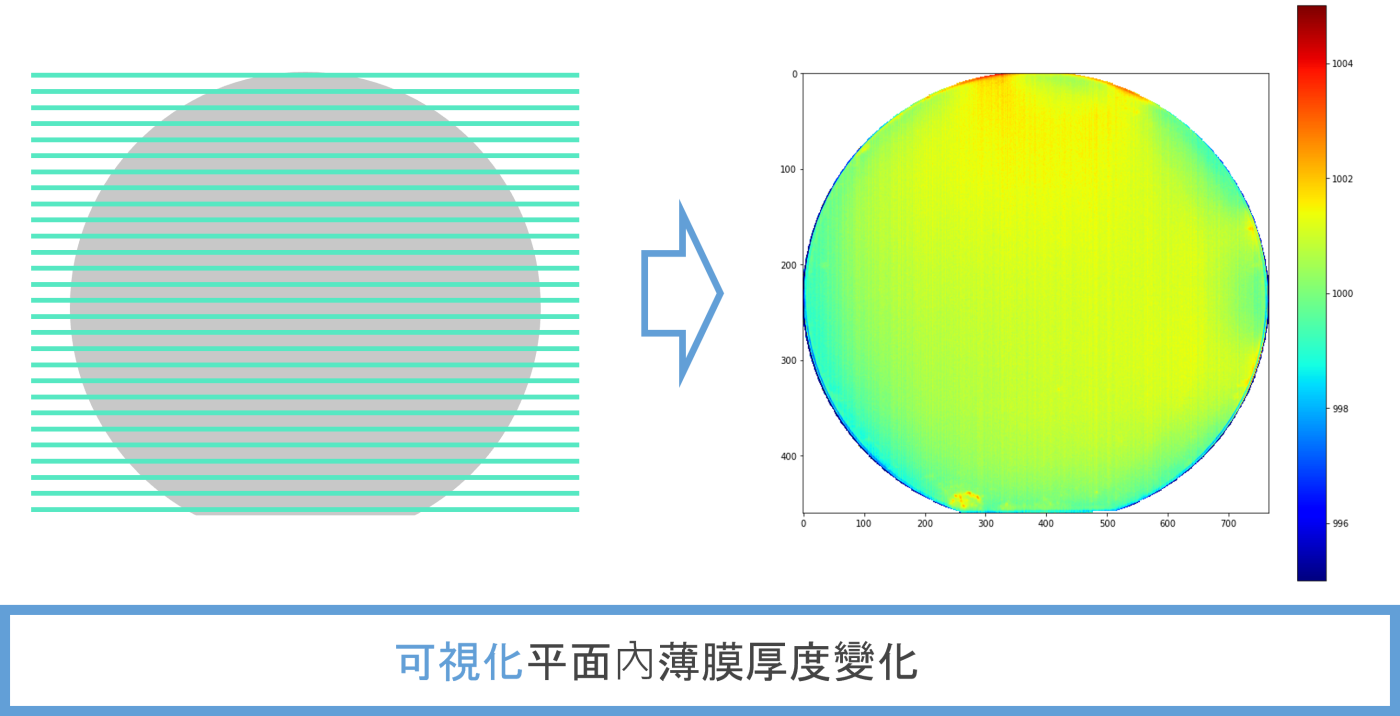

◎採用Line Scan方式,實現無"遺漏"的全面wafer檢查

採用單軸掃描進行全表面測量

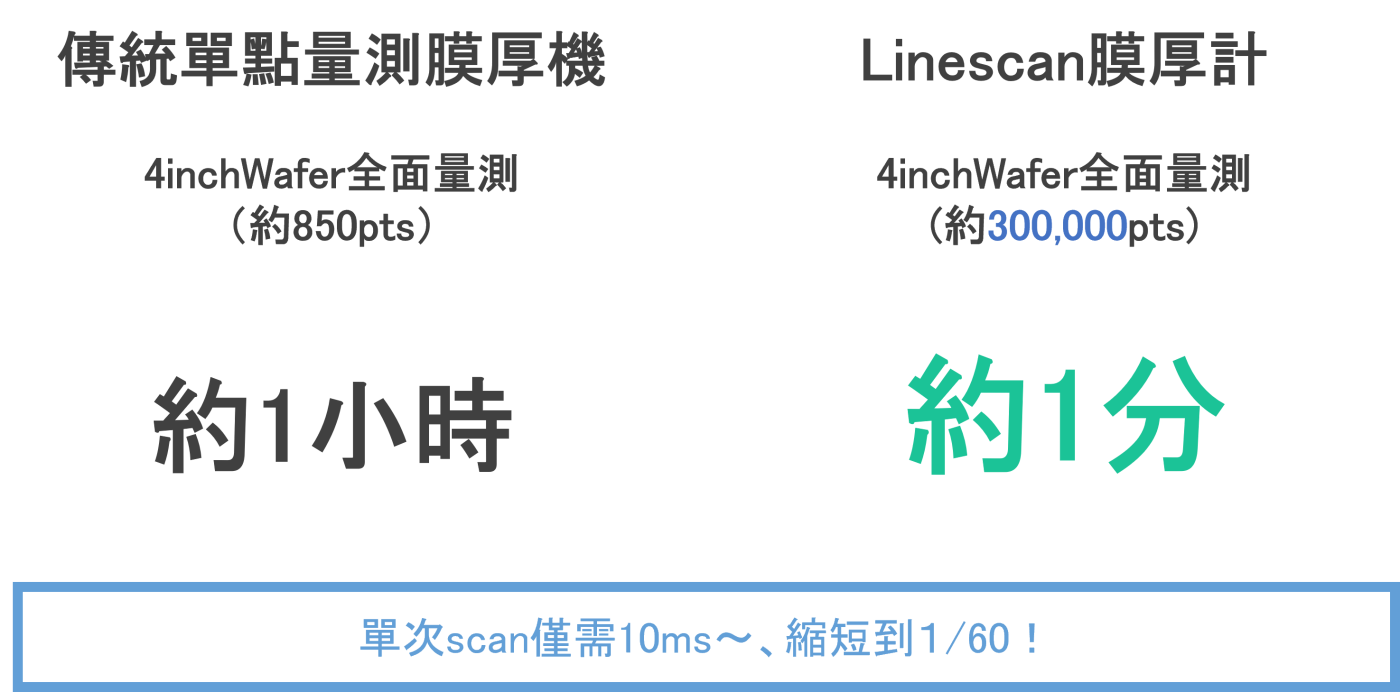

◎一瞬間Wafer全面檢查

LineScan方式的膜厚計,採用獨自開發的光干涉法的組合高速、高精度膜厚演算技術,實現最短0.01秒間隔。

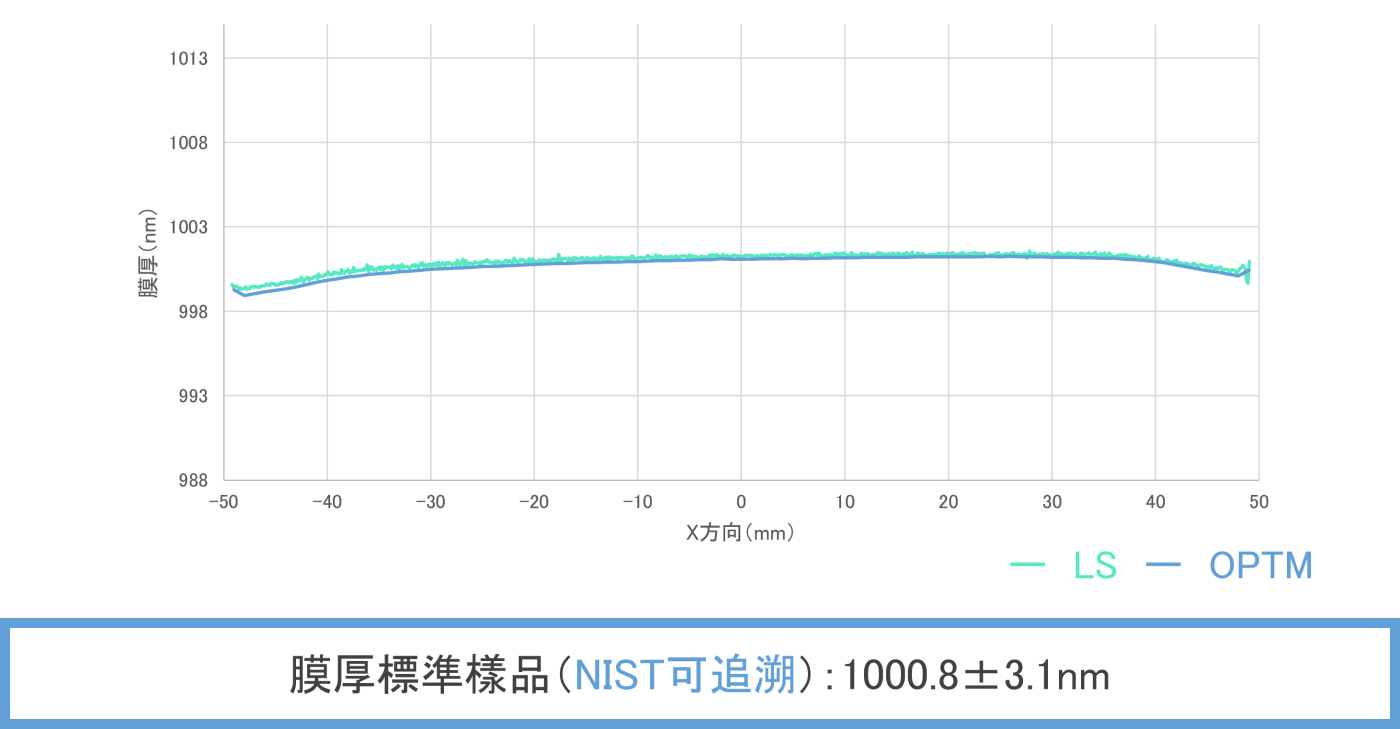

◎量測精度NIST安心朔源保證

LineScan量測實際案例 |

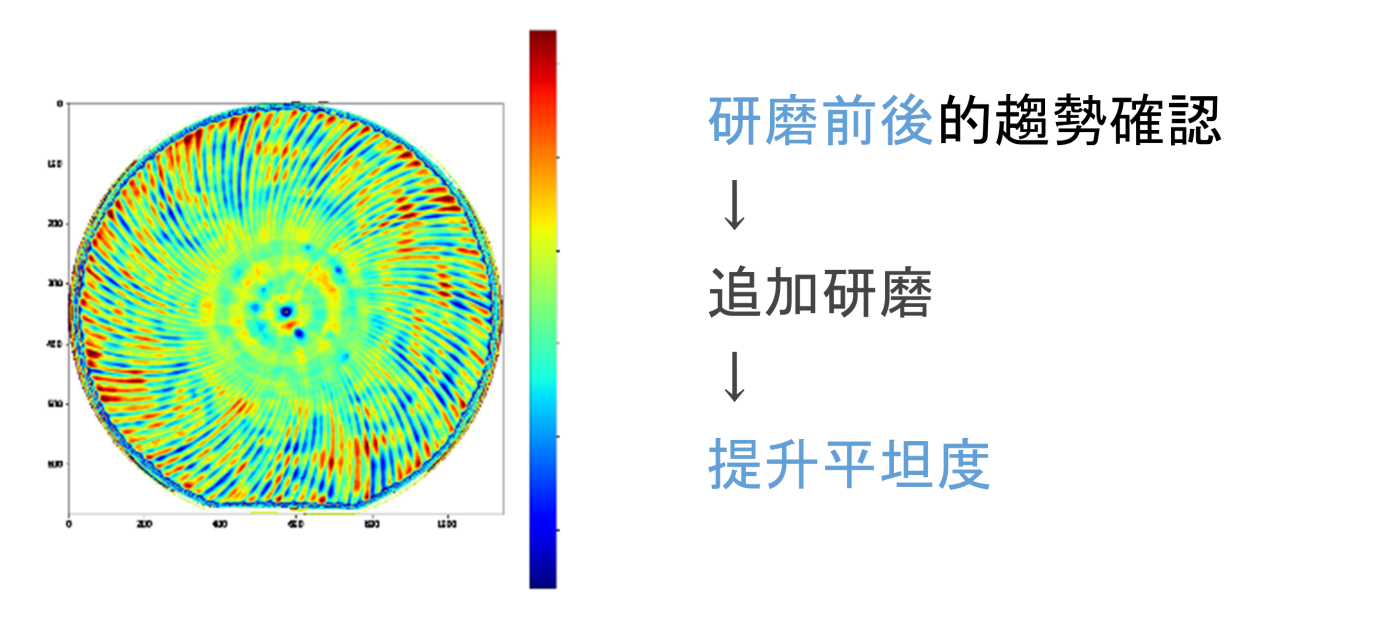

◎CMP拋光圖案清晰可見

可視化單點測量無法看到的微小不規則現象

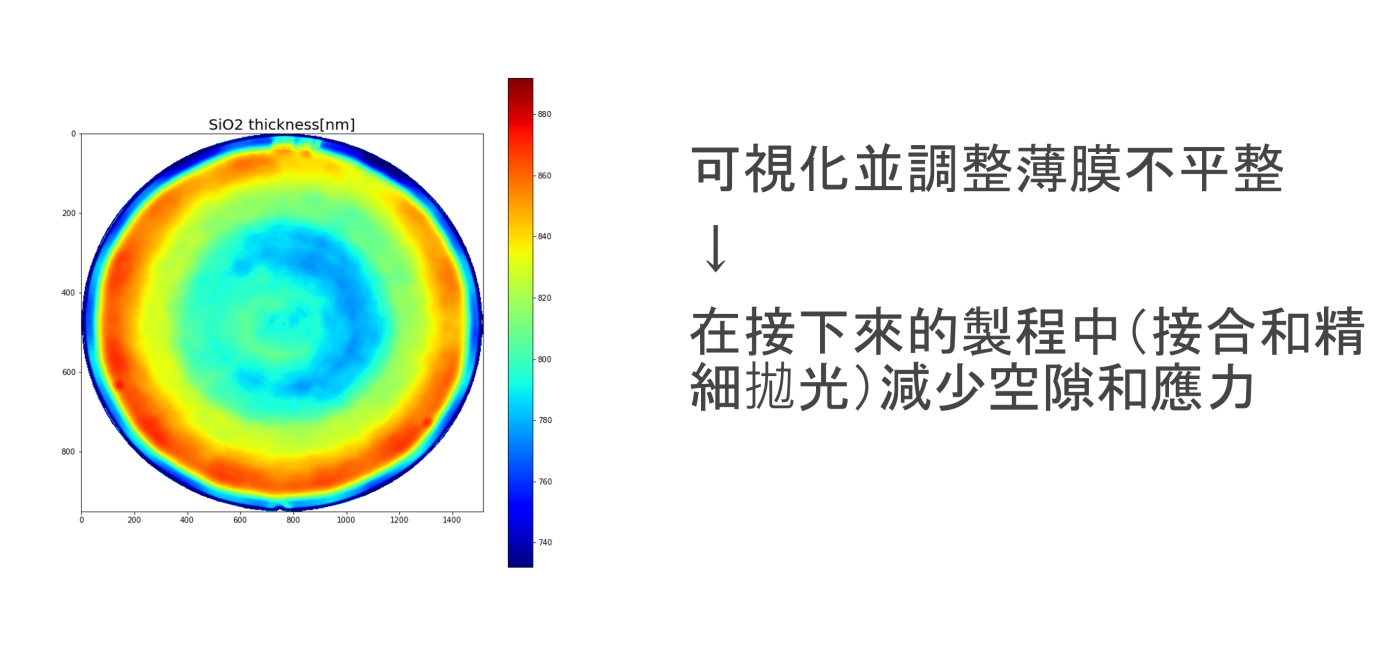

◎面內不平整度控管

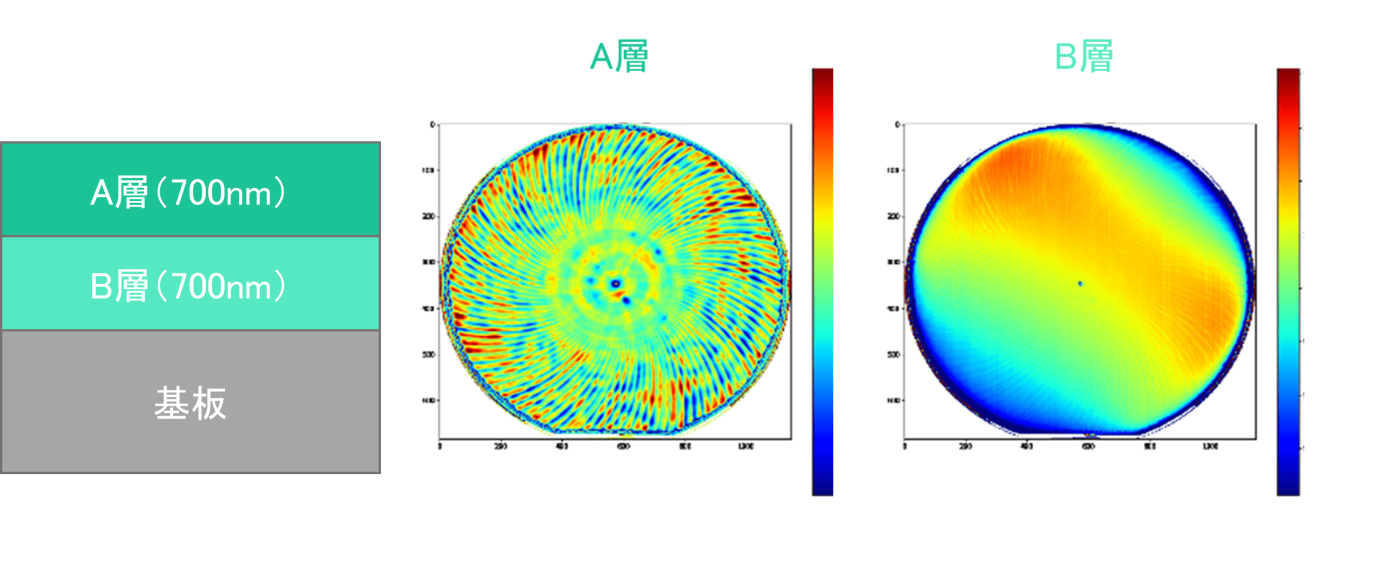

◎2層同時解析

可量測複數的膜層

規格樣式

| LineScan wafer檢測系統 | |

|---|---|

| 膜厚範圍 | 0.1um~300um |

| 對應wafer尺寸 | ~12inch |

| 量測間隔 | 10ms~ |

| 解析層數 | 對應多層解析(同時解析為2層) |

| 重複性(3σ) | 0.5nm以下 (1000nm樣品10次連續量測) |

| 膜厚精度 | 1000.8±3.1nm 合格 (NIST可追二次標準片) |

檔案下載

technical article

技術文章

-

25Mar.2025

半導體薄膜製程是什麼?6大技術提升良率,專業應用優勢多!

隨著科技的發展,對晶片效能的要求越來越高,這也對半導體薄膜製程提出了新的挑戰。你知道嗎?在微小的晶片上,需要層層堆疊極薄的材料,才能使這些薄膜的品質直接影響著晶片的效能和穩定性。如果你對於半導體薄膜製程還不是很清楚的話,不妨就一起跟著本文來了解半導體薄膜製程在不同領域的應用,是如何推動科技的發展與創新吧!

-

14Nov.2025

Wafer是什麼?前後2大半導體製程,帶你掌握晶圓的祕密!

許多人對於半導體產業不熟悉,尤其是對半導體製程的概念更是一知半解?!其實,主要是用來製作晶片的半導體製程,是需要透過一系列的專業步驟與搭配粒徑以及饃厚量測後,才能被完整的運用在各個產業之中。若你對於半導體製程還是有許多疑問的話,不妨就一起透過本篇專家的講解來了解吧!

-

06Dec.2022

CMP是什麼意思?Slurry製程深入介紹,清楚瞭解技術與原理!

CMP是什麼意思?製程中可應用在哪些環節?

讓你快速了解CMP製程的相關內容與應用!

Related Products